# Accélération matérielle de la vérification de sûreté et vivacité sur des architectures reconfigurables

Émilien Fournier

### ▶ To cite this version:

Émilien Fournier. Accélération matérielle de la vérification de sûreté et vivacité sur des architectures reconfigurables. Génie logiciel [cs.SE]. ENSTA Bretagne - École nationale supérieure de techniques avancées Bretagne, 2022. Français. NNT: 2022ENTA0006. tel-04109895

# HAL Id: tel-04109895 https://theses.hal.science/tel-04109895

Submitted on 30 May 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THÈSE DE DOCTORAT DE

### L'ÉCOLE NATIONALE SUPÉRIEURE DE TECHNIQUES AVANCÉES BRETAGNE

ÉCOLE DOCTORALE Nº 601

Mathématiques et Sciences et Technologies de l'Information et de la Communication

Spécialité: « Informatique »

Par

## **Emilien FOURNIER**

« Accélération matérielle de la vérification de sûreté et vivacité sur des architectures reconfigurables »

Thèse présentée et soutenue à « Brest », le « 05 Juillet 2022 » Unité de recherche : « Lab-STICC UMR CNRS 6285 »

### Rapporteurs avant soutenance:

Frédéric BONIOL Maître de Recherche HDR, ONERA, DTIS

Bertrand GRANADO Professeur des Universités, Sorbone Université, LIP6

#### **Composition du Jury:**

Président : Bertrand GRANADO Professeur des Universités, Sorbone Université, LIP6 Rapporteurs : Bertrand GRANADO Professeur des Universités, Sorbone Université, LIP6

Frédéric BONIOL Maître de Recherche HDR, ONERA, DTIS

Examinateurs : Virginie FRESSE Maître de Conférences HDR, Télécom Saint Etienne, Lab. Hubert Curien

Cécile BELLEUDY Maître de Conférences HDR, Université de Nice, LEAT Directeur de thèse : Loïc LAGADEC Professeur, HDR, ENSTA Bretagne, Lab-STICC

Encadrant de thèse : Ciprian TEODOROV Enseignant-Chercheur, ENSTA Bretagne, Lab-STICC

# REMERCIEMENTS

Je tiens à remercier tout d'abord mon encadrant, Ciprian Teodorov, à la fois pour la patience dont il a sû faire preuve, le soutien qu'il a pu m'offrir, mais également le savoir qu'il m'a transmis. J'ai pu ainsi, à ses côtés, m'épanouir techniquement et scientifiquement au cours de ces belles années.

J'adresse également toute ma reconnaissance à Loïc Lagagec, mon directeur de thèse, qui a toujours été à l'écoute pour m'orienter, et me conseiller, et définir les grands axes de mes travaux de recherche.

Mes remerciements vont également à Bertrand Granado et Frédéric Boniol, qui m'ont fait l'honneur de prendre le temps d'évaluer mes travaux en tant que rapporteurs. Je remercie Virginie Fresse et Cécile Belleudy d'avoir accepté de faire parti du jury. Je souhaite ensuite remercier Matthias Brun et Sebastien Pillement pour avoir participé à mon comité de suivi de thèse.

D'une manière plus générale, je veux remercier également mes collègues des équipes CS et SL, avec qui j'ai eu la chance de travailler, ainsi que plus généralement l'ensemble des personnels de l'ENSTA Bretagne qui m'ont accompagné dans mes activités d'enseignement et de recherche.

Malgré cet environnement favorable, l'aboutissement de ce travail de recherche n'aurait pas pû aboutir sans le soutien indéfectible de mes amis et de ma famille, qui m'ont guidé, soutenu, supporté - souffert? - pendant ces années aussi passionnantes que difficiles. C'est donc à vous que j'adresserai le mot de la fin : Cette réussite est aussi la votre, Merci!

# **TABLE OF CONTENTS**

| In | trod | uction   |                                                           | 9  |

|----|------|----------|-----------------------------------------------------------|----|

| 1  | Eta  | t de l'. | $\mathbf{Art}$                                            | 17 |

|    | 1.1  | Introd   | luction                                                   | 17 |

|    | 1.2  | Model    | -Checking                                                 | 17 |

|    |      | 1.2.1    | Principes du Model-Checking                               | 18 |

|    |      | 1.2.2    | Catégories de propriétés                                  | 20 |

|    |      | 1.2.3    | Vérification partielle                                    | 22 |

|    | 1.3  | Préser   | ntation synthétique des algorithmes                       | 25 |

|    |      | 1.3.1    | Formalisation abstraite des algorithmes d'atteignabilité  | 25 |

|    |      | 1.3.2    | Algorithmes exhaustifs                                    | 30 |

|    |      | 1.3.3    | Extension aux algorithmes de vérification partielle       | 36 |

|    | 1.4  | Enjeu    | x de performance et solutions matérielles                 | 38 |

|    |      | 1.4.1    | Plateformes de calcul parallèles pour le Model-Checking   | 38 |

|    |      | 1.4.2    | Accélération matérielle du Model-Checking                 | 40 |

|    |      | 1.4.3    | Synthèse                                                  | 42 |

|    | 1.5  | Concl    | usion                                                     | 43 |

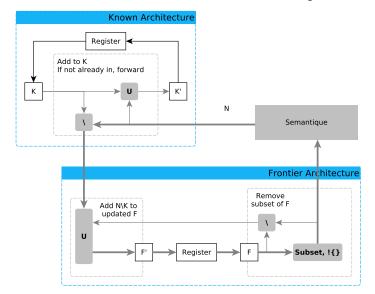

| 2  | Me   | nhir : 1 | Un cadre modulaire pour la vérification formelle sur FPGA | 45 |

|    | 2.1  | Archit   | secture fonctionnelle                                     | 46 |

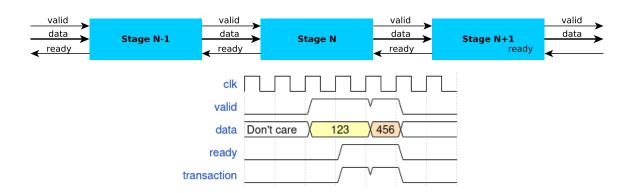

|    |      | 2.1.1    | Reformulation dataflow de la spécification                | 46 |

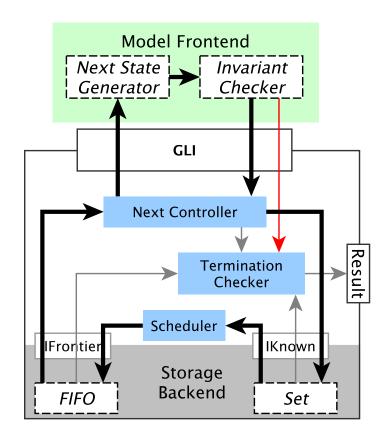

|    |      | 2.1.2    | Architecture générique abstraite                          | 49 |

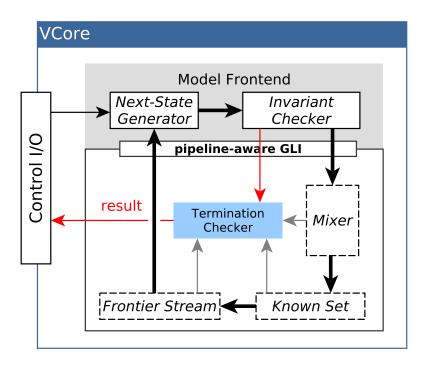

|    | 2.2  | Menhi    | ir : Un Model-Checker matériel modulaire                  | 52 |

|    |      | 2.2.1    | Overview                                                  | 52 |

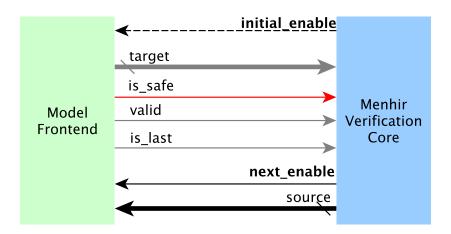

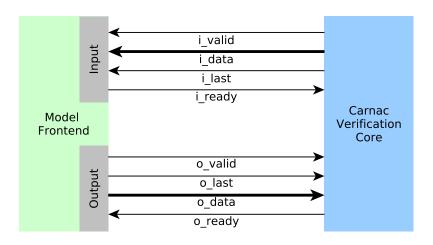

|    |      | 2.2.2    | Isoler le modèle du noyau de vérification                 | 56 |

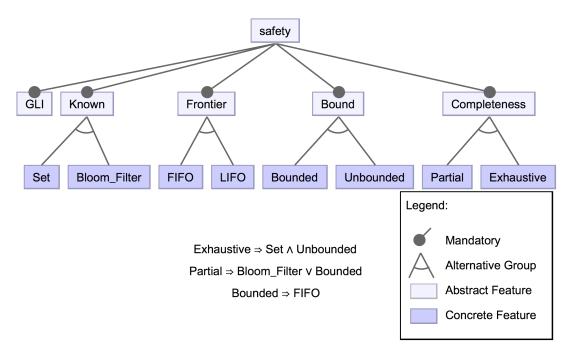

|    |      | 2.2.3    | Variabilité algorithmique du coeur de vérification        | 57 |

|    | 2.3  | Résult   | tats expérimentaux                                        | 61 |

|    |      | 2.3.1    | Mise en place de l'évaluation                             | 61 |

|    |      | 232      | Présentation des résultats                                | 63 |

### TABLE OF CONTENTS

|   | 2.4 | Conclu  | usion                                                             | 6' |

|---|-----|---------|-------------------------------------------------------------------|----|

| 3 | Car | nac : V | Variabilité algorithmique pour la vérification swarm efficace     | 69 |

|   | 3.1 | Explo   | ration de la variabilité algorithmique pour la vérification swarm | 7  |

|   |     | 3.1.1   | Exploiter la variabilité pour une plus grande diversification     | 7  |

|   |     | 3.1.2   | Métrique d'évaluation                                             | 75 |

|   | 3.2 | Résult  | ats expérimentaux                                                 | 76 |

|   |     | 3.2.1   | Configuration expérimentale                                       | 7  |

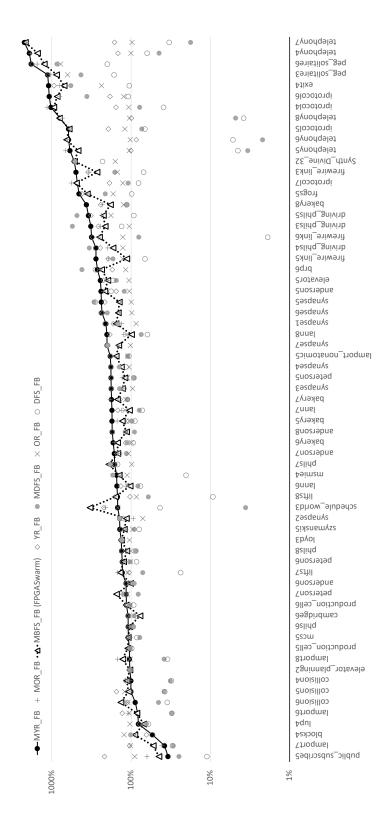

|   |     | 3.2.2   | Résultats de l'évaluation                                         | 8( |

|   |     | 3.2.3   | Synthèse                                                          | 8  |

|   | 3.3 | Carna   | c : Un moteur de vérification Swarm sur FPGA                      | 8. |

|   |     | 3.3.1   | Coeur de vérification                                             | 82 |

|   |     | 3.3.2   | Carnac : Architecture de contrôle - niveau Swarm                  | 8  |

|   | 3.4 | Evalua  | ation de l'implémentation matérielle                              | 8  |

|   |     | 3.4.1   | Configuration expérimentale                                       | 8  |

|   |     | 3.4.2   | Résultats                                                         | 88 |

|   | 3.5 | Conclu  | usion                                                             | 9( |

| 4 | D.I |         |                                                                   | ٠, |

| 4 |     |         | Un coeur swarm pour la vérification de sûreté et de vivacité      |    |

|   | 4.1 | Algori  |                                                                   | 94 |

|   |     | 4.1.1   | Algorithme de Courcoubetis                                        |    |

|   |     | 4.1.2   | Adaptation pour la vérification swarm                             |    |

|   |     | 4.1.3   | Complexité algorithmique                                          |    |

|   | 4.0 | 4.1.4   | Synthèse                                                          |    |

|   | 4.2 |         | secture                                                           |    |

|   |     | 4.2.1   | Architecture du coeur de vérification                             |    |

|   |     | 4.2.2   | Composition modèle - propriété                                    |    |

|   |     | 4.2.3   | Predicate checker                                                 |    |

|   |     | 4.2.4   | Génération de contre-exemples assistée par le logiciel            |    |

|   |     | 4.2.5   | Conclusion                                                        |    |

|   | 4.3 |         | ation                                                             |    |

|   |     | 4.3.1   | Méthodologie                                                      |    |

|   |     | 4.3.2   | Évaluation des performances                                       | 12 |

|   | 4.4 | Concli  | usion                                                             | 1: |

|  | TA | BI | $\mathcal{F}$ | OF | CO | NΓ | $\Gamma EI$ | NΠ | $\Gamma_{S}$ |

|--|----|----|---------------|----|----|----|-------------|----|--------------|

|--|----|----|---------------|----|----|----|-------------|----|--------------|

| Conclusion    | 115 |

|---------------|-----|

| Bibliographie | 121 |

# INTRODUCTION

#### Contexte

Les systèmes informatiques sont aujourd'hui omniprésents dans notre société, répondant à une multitude d'applications, depuis l'information jusqu'au transport et à la médecine. Ces systèmes sont de plus en plus complexes, offrant de plus en plus de fonctionnalités. Leur caractère interconnecté a introduit une modification drastique du fonctionnement de notre société. Notre dépendance à ces systèmes augmentant, le besoin de performances et de fiabilité est devenu un enjeu majeur, ces systèmes étant passés de l'ère des prototypes, au temps de l'industrialisation massive. Dans le même temps, cette croissance forte de la demande induit une réduction des délais alloués au développement, augmentant encore les contraintes sur ce processus.

Outre cette complexité de développement, les conséquences d'une faute peuvent être parfois dramatiques, et plusieurs erreurs logicielles sont restées dans les mémoires[1]. Un exemple parlant est celui du bug présent dans l'unité de division des entiers à virgule flottante de l'Intel Pentium, au début des années 90, qui a induit une perte estimée à 475 millions de dollars pour l'entreprise. Un autre est celui de l'explosion de la fusée Ariane 5, quelques dizaines de secondes après son premier lancement.

Pour maitriser cette complexité, les phases de vérification et de validation, correspondant respectivement à l'assurance de fiabilité et de fonctionnalité d'un système, ont fait l'objet d'un effort de recherche important, tant en termes d'outillage que de méthodologie. Parmi ces travaux, les méthodes formelles occupent une place particulière. Ces méthodes permettent en effet de s'affranchir du risque d'incomplétude des tests, en fournissant une preuve, au sens mathématique du terme, que le système respecte ses spécifications. Pour ce faire, il est d'abord nécessaire de formaliser le système de manière précise et non ambiguë, en s'affranchissant des obscurités du langage naturel. Le système est alors modélisé de manière intensionnelle - sous la forme d'un graphe implicite : Le système et son environnement d'exécution sont représentés sous la forme d'une relation de transition implicite, dont les états représentent l'ensemble des données nécessaires à l'évolution du système.

Une fois le système formalisé, débute la phase de vérification. Les outils formels sont nombreux pour l'effectuer, mais le Model-Checking constitue ici un premier choix par son caractère automatisé, et la variété de ses cadres d'application. Cette technique de preuve est très utilisée dans un contexte industriel, en particulier dans le cadre de la conception électronique, ou de la vérification de protocoles de communication. Clarke propose par exemple l'utilisation du Model-Checking pour la vérification d'unités arithmétiques et logiques, reproduisant le bug FDIV de l'Intel Pentium évoqué précédemment[2]. Newcombe décrit plus récemment son utilisation pour la vérification de systèmes distribués industriels[3]. Cette technique fournit une preuve par contre-exemple : L'espace des états atteignables du système est énuméré exhaustivement, en évaluant les propriétés de manière synchronisée. La terminaison de la preuve garantit ainsi l'absence des comportements redoutés.

Cette technique se heurte malheureusement à un problème de taille dans le cadre de la vérification de systèmes complexes : ajouter une variable booléenne double le nombre d'états potentiellement atteignables. Un effort de recherche très important a été déployé pour contrer cette caractéristique intrinsèque à la méthode, au travers de techniques d'abstraction, ou d'optimisation algorithmique[4][5]. Cependant, le caractère exponentiel de l'explosion combinatoire en fait un enjeu toujours critique, car dans le cas de problèmes toujours plus complexes, la taille de l'espace d'état ne permet pas de terminer la preuve.

Plusieurs approches sont mobilisables pour contrecarrer ce problème, que l'on peut catégoriser en fonction de leur caractère sémantique ou algorithmique. Sur le plan sémantique, l'objectif est de réduire la complexité du modèle vérifié abstrayant le système, ne formalisant dans le modèle vérifié que les comportements relatifs à la preuve en cours tout en restant complet. De manière orthogonale mais complémentaire, des techniques algorithmiques visent à améliorer la scalabilité et la performance des outils. De manière générale, le problème adressé par la communauté dans ce cadre est la vérification de modèles plus grands pour un même budget en temps et en mémoire.

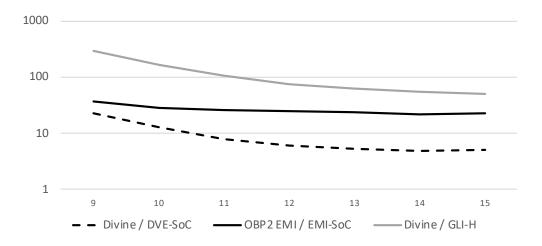

Dans ce cadre, l'accélération matérielle constitue une opportunité prometteuse. Des travaux de recherche récents revendiquent en effet une amélioration importante tant des performances que de la scalabilité pour la vérification swarm pour la sûreté[6], technique partielle basée sur l'exécution massive d'analyses partielles randomisées, produisant un facteur d'accélération proche de trois ordres de grandeur par rapport à une implémentation logicielle performante[7]. Ces travaux sont cependant à un stade exploratoire, et reposent sur une évaluation sur un cas d'étude unique, évalué sur une architecture monolithique dédiée à l'exécution d'un algorithme précis.

### Questions de recherche

Dans ce contexte, l'enjeu global adressé ici est l'exploration des opportunités de l'accélération matérielle du Model-Checking sur des architectures reconfigurables.

Cette problématique se traduit par plusieurs aspects. Un premier est illustré par l'état actuel de la littérature sur le sujet. Malgré des gains de performance supérieurs de plusieurs ordres de grandeurs aux meilleures implémentations parallèles logicielles[6], seuls deux travaux - espacés d'une décennie - proposent l'exploitation de FPGAs pour l'accélération du Model-Checking. Nous interprétons celà par plusieurs fondements. Le premier est de toute évidence la complexité de conception d'une telle solution, cette complexité se traduit également dans les résultats proposés, difficiles à comparer et à mettre en perspective, élément essentiel pour permettre une démarche de recherche incrémentale et structurée sur le sujet. En outre, le caractère exploratoire actuel des travaux sur le sujet rendent difficile la perspective de l'exploitation à court terme d'une telle technologie dans un outil de vérification.

Un autre axe de complexité est introduit par la multiplicité des algorithmes et des langages de spécification existants, nécessaires pour adapter les choix effectués dans le plan de vérification d'un système aux caractéristiques du problème étudié. Ces choix se traduisent en pratique en l'utilisation d'un langage de spécification adapté au niveau d'abstraction du modèle étudié, ainsi que par l'utilisation des algorithmes adaptés aux contraintes en termes de ressources mémoires et temporelles.

Ces deux axes se rejoignent par le besoin de réduction de la complexité d'un tel développement. Cette complexité provient d'un manque de cadre architectural et méthodologique pour la conception de tels accélérateurs, y répondre constitue une première question adressée par ce manuscrit.

Parmi les applications de l'accélération matérielle pour le Model-Checking, la vérification swarm se détache en termes de performance. Cette technique s'accommode en effet d'un faible volume mémoire et bénéficie d'un double niveau de parallélisme - de tâches, mais également à l'échelle locale d'une tâche de vérification - en faisant un candidat idéal pour l'accélération matérielle. Cependant, le caractère indépendant et randomisé des taches de vérification induit un recouvrement entre les sous-ensembles de l'espace d'état parcouru par chacune d'entre elles. Ce recouvrement induit une forte déperdition de l'effort de vérification, certaines sections de l'espace d'état étant parcourues plusieurs fois. L'enjeu scientifique considéré ici est l'augmentation de l'efficacité des algorithmes de vérification swarm, par la réduction de cette duplication de travail. Un second enjeu allant

de pair pour l'accroissement des performances de la vérification swarm est la conception d'un coeur de vérification correspondant au cadre abstrait proposé, mais optimisé pour la performance.

La spécification d'un système se construit autour de deux classes de propriétés, énoncées par Lamport en 77 : sûreté et vivacité[8]. Cette catégorisation correspond respectivement à la formalisation de comportements proscrits et prescrits du système, mais définit également l'expressivité du formalisme nécessaire pour la vérification. Ce formalisme va de pair avec les algorithmes pour les vérifier, pouvant se réduire à une analyse d'atteignabilité dans le premier cas, mais nécessitant une détection de cycles dans le deuxième.

A ce jour, les travaux portant sur l'accélération matérielle du Model-Checking se limitent au support de la vérification de propriétés de sûreté. Une autre question de recherche étudiée ici est comment concevoir une architecture de vérification matérielle pour la vérification d'automates de Büchi, formalisme permettant la vérification de propriétés de vicacité. Une question en découlant immédiatement est celle de la reproductibilité des performances obtenues pour la vérification de sûreté dans le cadre de la vérification de propriétés de vivacité.

Enfin, un enjeu plus ouvert est celui de la réutilisation des sémantiques existantes. L'introduction d'une nouvelle architecture de calcul pour la vérification pose en effet la question de l'utilisabilité des langages conçus pour les plateformes de calcul actuelles. Il s'agit donc ici de s'intéresser à la réutilisation de ces langages de spécification existants pour la vérification accélérée en matériel.

#### Contributions

La première contribution présentée dans ce manuscrit pour apporter des éléments de réponse aux questions de recherche énoncées ci-avant est le framework de vérification matériel Menhir. Un élément structurant de cette architecture de vérification matérielle est l'introduction d'une interface langage générique, permettant une division forte du problème de conception entre le coeur algorithmique et un *model-frontend*, encapsulant la sémantique du modèle vérifié et de ses propriétés associées. Son architecture générique et modulaire permet une forte variabilité tant dans la représentation de l'information stockée, que dans la discipline de parcours de l'espace d'état du modèle.

La généricité de cette architecture est illustrée au travers de l'implémentation de 6 algorithmes de vérification, formant un dégradé depuis la vérification exhaustive vers des analyses partielles de l'espace d'état. En outre, l'isolation forte entre la sémantique du

modèle et l'algorithme de vérification permet l'intégration - transparente pour le coeur algorithmique - de trois langages d'entrée couvrant la vérification de modèles exprimés dans un formalisme industriel comme UML, jusqu'à des modèles de très bas niveau, spécifiés directement en RTL.

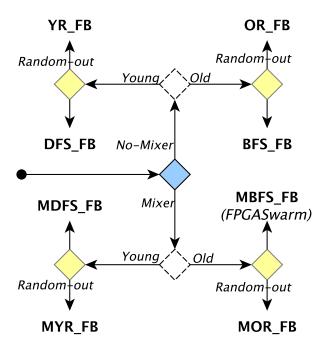

Dans un second temps, cette généricité est exploitée pour adresser le problème d'efficacité des algorithmes de vérification swarm au travers d'une exploration de l'espace de conception algorithmique. Cette étude théorique se traduit par la proposition d'un nouvel algorithme randomisé de vérification swarm, minimisant à la fois le recouvrement des analyses et l'utilisation mémoire induite pour d'adapter aux contraintes d'implémentation des architectures reconfigurables.

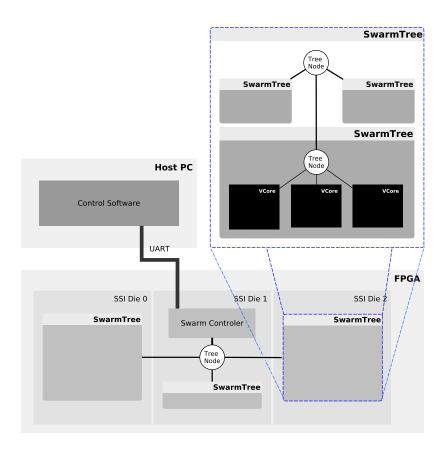

Dans le but de maximiser la performance globale de la vérification swarm, pour laquelle l'efficacité va de pair avec la performance brute de la plateforme d'exécution. L'architecture de vérification distribuée Carnac adresse ces deux points, implémentant l'algorithme de vérification identifié au sein d'un coeur de vérification qui constitue une réinterprétation de l'approche générique Menhir, spécialisée pour la performance. La structure distribuée de Carnac contribue de plus à la scalabilité de l'approche, permettant l'intégration d'un grand nombre de coeurs de vérification sur des FPGAs multi-die.

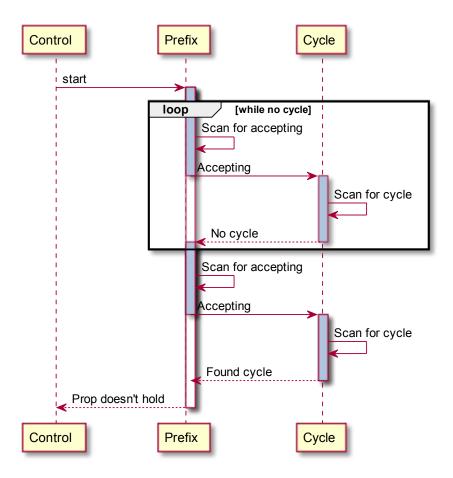

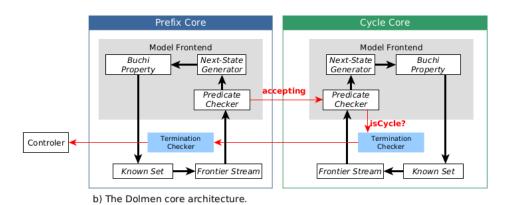

Le troisième enjeu identifié est constitué par la vérification des propriétés de vivacité. Un élément de réponse est apporté ici par la proposition d'un algorithme swarm pour la vérification de propriétés de sûreté et de vivacité encodées sous la forme d'automates de Büchi, adapté aux contraintes imposées par une implémentation matérielle. Une preuve de faisabilité est ensuite constituée par l'implémentation du coeur de vérification Dolmen pour la détection de cycles d'acceptation dans les automates de Büchi, réorientation du coeur de vérification Carnac, illustrant ainsi sa généralité.

D'une manière transverse, plusieurs éléments de réponse sont apportés sur le plan de la réutilisation sémantique : Le support des langages UML et DVE par le moteur de vérification Menhir en est un, démontrant la faisabilité d'une approche hybride FPGA-CPU. Les performances potentielles de cette approche restent cependant un sujet ouvert. Une autre solution potentielle est explorée, sous la forme d'un outil de génération de circuit à partir du langage de spécification DVE. Cette approche atteint les attendus en termes de performance, mais l'utilisation importante des ressources doit faire l'objet d'améliorations.

#### Plan du manuscrit

Le chapitre 1 présente des éléments de l'état de l'art de la vérification par Model-Checking. Après avoir exposé les principes de cette technique de vérification, nous proposons une formulation abstraite des algorithmes de vérification de sûreté sous la forme d'une spécification formelle. Enfin, l'enjeu de performance des outils est discuté, présentant des travaux existants visant la parallélisation du Model-Checking sur les architectures de calcul modernes.

Cette spécification est ensuite reformulée dans le chapitre 2 pour construire une architecture générique abstraite d'un moteur de vérification matériel, et identifier les dépendances de données pour cet ensemble d'algorithmes. Cette abstraction est exploitée comme guide de conception pour l'architecture du moteur de vérification matérielle Menhir, dont la structure modulaire se veut agnostique tant aux algorithmes implémentés qu'aux sémantiques vérifiées. Cette généricité est illustrée par l'implémentation de 6 algorithmes de vérification pour la sûreté, et de trois sémantiques, proposant un dégradé d'abstraction depuis des langages de spécification industriels comme UML, jusqu'à des implémentations dédiées exprimées en RTL.

Le chapitre 3 adresse le problème de l'efficacité des algorithmes swarm, en exploitant la variabilité algorithmique exposée dans le chapitre précédent pour conduire une exploration de l'espace de conception algorithmique qui vise à minimiser le recouvrement entre les tâches de vérification, et maximisant ainsi la couverture à effort de calcul constant. Cette étude théorique mène à l'identification d'un nouvel algorithme de vérification swarm, intégré à l'architecture de vérification Carnac sous la forme d'un coeur dédié, réinterprétation de l'approche générique Menhir visant à maximiser la performance à l'exécution. L'intégration de ce coeur au sein d'une architecture scalable, conçue réduire les contraintes de localité des données propres aux FPGA multi-die. L'analyse théorique effectuée sur l'efficacité algorithmique est consolidée par une évaluation expérimentale sur un cas d'étude de référence pour la vérification swarm matérielle.

Pour finir, la vérification de propriétés de vivacité est adressée dans le chapitre 4. Dans ce cadre, nous proposons un algorithme swarm pour la vérification de propriétés de sûreté et de vivacité exprimées sous la forme d'automates de Büchi. Cet algorithme est implémenté sous la forme du coeur de vérification Dolmen, qui, en couplant deux coeurs de vérification proposés précédemment, effectue une détection de cycles d'acceptation. Outre l'illustration de la généralité de l'architecture du coeur Carnac proposée précédemment, cette implémentation permet également de confirmer l'analyse théorique effectuée pour

contruire l'algorithme, au travers d'une évaluation effectuée sur un ensemble de modèles représentatifs des cas d'études classiques adressables par Model-Checking.

Le dernier chapitre conclue ce manuscrit, et présente des perspectives pour des travaux futurs selon deux axes principaux : sémantique et algorithmique.

### Liste des publications

- [1] E. FOURNIER, C. TEODOROV et L. LAGADEC, « Carnac : Algorithm Variability for Fast Swarm Model-Checking on FPGA », in 2021 31th International Conference on Field Programmable Logic and Applications (FPL'21), août 2021, p. 185-189. DOI: 10.1109/FPL53798.2021.00038.

- [2] E. FOURNIER, C. TEODOROV et L. LAGADEC, « Menhir : Generic High-Speed FPGA Model-Checker », in 2020 23rd Euromicro Conference on Digital System Design (DSD), 2020, p. 65-72. DOI: 10.1109/DSD51259.2020.00022.

- [3] E. FOURNIER, C. TEODOROV et L. LAGADEC, « Dolmen : FPGA Swarm for Safety and Liveness Verification », in 2022 Design, Automation and Test in Europe Conference Exhibition (DATE'22), 2022.

# ETAT DE L'ART

### 1.1 Introduction

La phase de vérification est une composantes les plus importantes du processus de conception d'un système. De plus, la complexité croissante de ces derniers conduit à une augmentation drastique tant de la criticité, que de la probabilité d'occurrence d'erreurs. Pour détecter et corriger ces erreurs, différents types d'analyse peuvent être mises en oeuvre. Certaines, dites formelles, visent à fournir une preuve au sens mathématique du terme qu'un système - ou une abstraction de ce dernier - satisfait certaines propriétés, qui modélisent sous une forme précise et non ambiguë les spécifications à respecter par le système. Parmi les techniques de vérification formelles, ce travail aborde le Model-Checking, technique de preuve par contre-exemple automatique. Cette technique effectue une recherche de contre-exemple sur l'ensemble des états atteignables d'un système, permettant ainsi de garantir leur absence.

Ce chapitre présente dans un premier temps le formalisme utilisé pour la vérification par Model-Checking, puis propose une vue abstraite des algorithmes de vérification pour la sûreté, sous la forme d'une spécification. Enfin, l'enjeu de la performance des outils de vérification est discuté par une description des approches proposées pour l'implémenation d'outils de vérification parallèles.

# 1.2 Model-Checking

Après avoir défini la formalisation du problème de vérification utilisée dans le cadre d'une preuve par Model-Checking, cette section discute de l'expression des propriétés vérifiées, avant d'introduire des techniques permettant d'accroître la scalabilité de la méthode.

Pour plus de détails, le lecteur peut se référer à l'ouvrage Principles of Model-Checking[1].

### 1.2.1 Principes du Model-Checking

Le Model-Checking est une technique de vérification qui a été proposé de manière simultanée et indépendante au début des années 80 par les travaux de Clarke et Emerson [9] et ceux de Sifakis et Queille [10].

Cette approche constitue une technique de preuve générique et automatisée, basée sur l'analyse systématique de la validité des propriétés vérifiées sur l'ensemble des états atteignables d'un système. Cet ensemble est désigné par le terme espace d'état. Son applicabilité est basée sur l'hypothèse que le système vérifié, qui se présente sous la forme d'une relation de transition, peut être énuméré exhaustivement.

Cette hypothèse est vérifiée naturellement dans le cadre de la vérification d'un système informatique ou numérique concret. Cependant, dans le cas d'un système complexe, élaborer la preuve directement est souvent une tâche trop complexe, voire impossible en pratique. Ainsi, la preuve est construite - en général - non pas sur le système lui-même, ie son implémentation, mais sur une abstraction de ce dernier. L'abstraction d'un système permet de réduire la taille de l'espace d'état à vérifier, en construisant un modèle abstrait, cachant certains détails d'implémentations. Cette abstraction n'est pas toujours réalisée, et la vérification est parfois effectuée directement sur le programme implémenté [11], cependant, dans le vocabulaire associé au Model-Checking, le terme Modèle est utilisé pour désigner l'objet de la vérification.

Le *Modèle* vérifié prends la forme d'un système de transitions. Les noeuds de ce graphe représentent les différents états du système, et les arcs - ou transitions - désignent les pas d'exécutions effectués pour faire évoluer le système d'un noeud à un autre. L'état d'un système doit être compris comme l'ensemble de ses variables, ainsi que l'endroit du programme où on est arrivé (*program counter*). Ce dernier contient l'ensemble de l'information suffisante pour restaurer l'exécution du programme dans les conditions exactes dans lesquelles ce dernier a été interrompu. Dans la suite, le terme configuration désigne l'état du système vérifié et de son environnement.

Aussi, le modèle vérifié peut être interprété comme un simple graphe, contenant des noeuds, et des transitions. Ce graphe possède un, ou plusieurs états initiaux, représentant les états d'initialisation possibles du système. Ce graphe n'est pas nécessairement déterministe. Cette idée peut paraître contre-intuitive, dans la mesure où le système vérifié peut être un programme réel, dont l'exécution est déterministe. Cependant, dans le cadre d'une tâche de vérification par Model-Checking, le système vérifié est dit fermé, et ne possède donc ni entrées ni sorties. Dans le cas de la vérification d'un programme possédant

des entrées-sorties, la vérification porte sur le système évoluant dans son environnement d'exécution, qui produit les entrées, et lit les sorties. Une conséquence directe, intrinsèque à la méthode, est que la vérification par Model-Checking ne vérifie le système que relativement à son environnement. Dit autrement, le programme n'est vérifié qu'au regard des sollicitations décrites dans cet environnement[12].

Les propriétés vérifiées sont exprimées dans des langages de spécification de haut niveau. De multiples langages peuvent être utilisés, suivant le besoin d'expressivité de la tâche de vérification en question. Les langages de spécification sont basés sur des formalismes mathématiques plus expressifs que les expressions booléennes, comme la logique temporelle linéaire LTL, ou la logique temporelle arborescente CTL. Dans un contexte industriel, les langages utilisés pour la vérification combinent parfois plusieurs logiques pour permettre la couverture d'un maximum de cas d'usage : on peut citer les langages PSL et SVA, très utilisés pour la vérification de circuits [13][14].

Le langage utilisé pour l'expression des propriétés n'est pas interprété directement. En amont d'une tâche de vérification, les propriétés sont reformulées sous la forme d'un automate fini, de manière homogène à la représentation du modèle vérifié. Cet automate représente la négation de la propriété à vérifier sur le modèle.

Aussi, les mots acceptés par l'automate représentant la propriété correspondent à des contre-exemples de la propriété vérifiée.

Le problème de Model-Checking est formalisé de la manière suivante : Soit un modèle M décrit sous la forme d'un automate fini non déterministe, et une formule à vérifier f exprimée dans une logique temporelle. La vérification s'effectue de la manière suivante : [15]

- Construction de l'automate fini non déterministe représentant la négation de la formule f. Un mot accepté par cet automate corresponds alors à un mot qui met en défaut la propriété. On note cet automate  $A_{\neg f}$ .

- Composition synchrone de l'automate représentant le modèle M et de la propriété  $A_{\neg f}$ . Un mot accepté par l'automate résultat est alors accepté simultanément par le modèle et la propriété.

- Vérification que l'automate résultat n'est pas vide.

Cette formulation du problème de Model-Checking se veut générique et didactique. Cependant, la construction de l'automate produit précédent la vérification nécessite un volume mémoire important pour stocker cet automate. Edmund Clarke, l'un des initiateurs du Model-Checking, fait remarquer à ce sujet que la composition asynchrone de n

processus, chacun possédant m états, peut avoir dans le pire des cas  $m^n$  états [5]. En pratique, l'approche moderne consiste plutôt à effectuer la composition à la volée, pendant l'exploration, permettant d'éviter cet écueil, ce qui permet de conclure d'une violation des spécifications avant la construction complète du produit. Néanmoins, si la propriété n'est pas violée, le parcours de l'espace d'état reste exhaustif.

### 1.2.2 Catégories de propriétés

Le Model-Checking est une technique de vérification basée sur la vérification de propriétés, représentant des exigences que le programe doit respecter. Cette approche présente l'intérêt d'être à la fois abstraite et modulaire. Son caractère abstrait se traduit par le fait que la spécification est traduite en une liste de propriétés indépendantes les unes des autres, sans avoir à se soucier de comment elles intéragissent entre elles, évitant ainsi de sur-spécifier le système. Son caractère modulaire se traduit par le fait qu'une liste de propriétés, qui traduit la spécification, peut aisément être modifiée par l'ajout, ou le retrait de l'une d'entre elles.

Cependant, ce caractère à la foit abstrait et modulaire de la spécification de systèmes par la définition de propriétés formelles présente un risque de sous-spécification. Une question classique se posant lors de la spécification d'un système est sa complétude : La liste de propriétés est-elle suffisante pour traduire la spécification? Un exemple simple de sous-spécification, proposé par Manna en 1990, est celui de la spécification d'un algorithme d'exclusion mutuelle. Une spécification faussée consisterait à s'assurer que les deux processus n'accèdent pas à la section critique de manière simultanée, sans préciser la nécessité qu'un des processus accède au moins une fois à la section critique [16]. Une implémentation fausse, mais qui respecterait la spécification, serait alors d'implémenter un algorithme dans lequel aucun des deux processus n'accède jamais à la section critique.

Une solution partielle, proposée par Lamport en 1977[17], à ce problème de sous-spécification consiste à classifier les propriétés rôle dans l'élaboration de la spécification, selon deux catégories : Sûreté et Vivacité . Cette catégorisation a depuis été raffinée, par Manna et Pnueli, qui proposent une hiérarchie des propriétés de vivacité [16]. Cependant, la classification de Lamport sera utilisée dans la suite. Bien que moins fine, elle présente l'intérêt de correspondre aux besoins algorithmiques pour les vérifier.

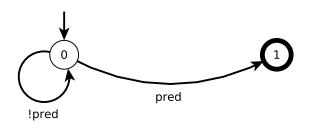

FIGURE 1.1 - NFA représentant une propriété portant sur un état - l'état 1 est un état d'acceptation

### Propriétés de sûreté:

Une première classe de propriétés, dites de sureté, visent à exprimer des comportements non désirés du système. Elles sont formalisées sous la forme de prédicats, portant sur un chemin fini dans l'espace d'état du système. Elles sont modélisées sous formes d'automates finis non déterministes, dont certains états sont définis comme "acceptants", ie, caractérisent la fin d'un mot reconnu par l'automate. La section précédente - 1.2.1 - formalise le problème de Model-Checking comme une tâche vérifiant que le langage résultant de la composition synchrone du modèle et de la propriété vérifiée est vide. Aussi, pour vérifier des propriétés de sureté, il suffit de détecter l'absence d'états d'acceptation dans l'automate produit par la composition de la propriété avec le système. Les assertions portant sur un état, vérifiant qu'un état seul respecte un prédicat, sont une sous-classe triviale de propriétés de sûreté, dont le NFA est représenté dans la figure 1.1 ci-après.

#### Propriétés de vivacité

Pour construire une spécification complète d'un programme, après avoir modélisé les comportements non désirés, il est nécessaire de modéliser les comportements désirés du système: Un programme qui ne fais rien ne contient pas de fautes. Pour cela, on utilise un second type de propriétés, dites de vivacité. Ces propriétés peuvent se comprendre comme "Le système fera toujours ... ". Pour vérifier une telle propriété par contre exemple, il est nécessaire de prouver que "le système ne fera jamais ... ". Une telle assertion n'est pas vérifiable sur un chemin fini : Si un chemin fini est "sur", une faute pourra se trouver "plus tard" dans l'exécution. Aussi, il est nécessaire de raisonner sur des chemins infinis, au sein d'un graphe fini, qui ne peuvent alors n'être que des cycles.

Plus précisément, ces propriétés sont modélisées via des automates dont la structure est similaire aux NFA, mais dont l'interprétation est très différente. Les automates de Büchi, utilisés pour modéliser les propriétés de vivacité, sont des automates non déterministes, comportant des états particuliers, désignés également comme états d'acceptation. Cependant, dans le cas des automates de Büchi, un mot n'est accepté que s'il contient un état d'acceptation infiniment souvent. Une des hypothèses du Model-Checking étant que l'espace d'état est fini, un tel état doit nécessairement faire partie d'un cycle.

Aussi, dans une formulation intuitive, la construction d'un contre-exemple pour des propriétés de vivacité consiste à détecter des cycles, contenant un état d'acceptation. On peut ainsi reformuler le problème de conception d'une architecture de vérification de propriétés de vivacité, en un problème de conception d'une architecture de détection de cycles dans un graphe.

### 1.2.3 Vérification partielle

Le Model-Checking est une technique de vérification automatisée basée sur une analyse systématique de l'espace-d'état correspondant à l'exécution du modèle sous-jacent. Cette technique est basée sur une énumération exhaustive de la relation de transition qui représente le modèle composé avec sa propriété. L'espace d'état est un graphe potentiellement cyclique. Aussi, son parcours nécessite d'accumuler les états parcourus au cours de l'exploration pour assurer la terminaison de l'algorithme.

Ce stockage de l'espace d'état est potentiellement très couteux en ressources mémoire. Pour des modèles complexes, il est fréquent que la preuve ne puisse pas terminer, par manque de mémoire disponible, le besoin mémoire étant exponentiel en le nombre de variables représentées dans le système (dans le pire des cas). Cette caractéristique intrinsèque à la méthode est souvent désignée par le terme d'explosion combinatoire, state-space explosion en anglais[5].

La recherche de solutions pour repousser ce problème d'explosion combinatoire a été un moteur majeur de la recherche sur le Model-Checking [5]. Des travaux riches ont été conduits dans le but de réduire le besoin mémoire d'une tâche de Model-Checking par des techniques d'abstraction automatique [18], symboliques [19], ou exploitant l'indépendance de certains évènements pour éviter l'exploration de certaines transitions [4].

### Approches partielles: bitstate hashing, hash-compaction

Les approches précédentes visent à augmenter la scalabilité du Model-Checking par des approches sans perte de données. Pour aller plus loin, et augmenter encore la scalabilité du Model-Checking, plusieurs techniques ont été proposées, reposant sur des techniques de compression avec perte pour stocker l'espace d'état de manière extrêmement compacte. Proposant un compromis entre couverture de l'espace d'état et scalabilité par rapport aux méthodes classiques, ces approches proposent l'utilisation d'une représentation probabiliste d'ensemble pour stocker l'espace d'état. Ce type de représentation peut introduire, contrairement à une représentation déterministe, des faux positifs lors de la requête d'appartenance à l'ensemble, qui implique alors que l'espace d'état n'est plus nécessairement parcouru exhaustivement. Aussi, l'absence d'erreur n'est plus garantie formellement, dans la mesure où il n'est plus garanti que l'espace d'état a été parcouru dans son intégralité. Cependant, la réduction très significative de l'espace mémoire requis en font une approche très utilisée pour la vérification de systèmes réels complexes. Ces approches incluent des techniques comme le bitstate hashing, qui exploite un filtre de Bloom pour stocker l'espace d'états, ou hash compaction, se basant sur une table de hachage pour stocker les hash des états parcourus, en lieu et place de leur forme complète [20][21][22].

#### Vérification swarm

Lors d'une tâche de vérification par bitstate-hashing, la couverture, que l'on peut définir comme la proportion de l'espace d'état couverte par une tâche de vérification, n'est pas totale. Seule une partie de l'espace d'état est vérifié par une tâche de vérification. Cette partition est définie par la discipline adoptée pour le parcours de l'espace d'état : BFS ou DFS, ainsi que par la - ou les - fonctions de hachage utilisées par le Bloom filter pour stocker l'espace d'état. Ce sont en effet les collisions occurant dans le Bloom filter qui sont à l'origine de l'élimination de certaines sous-parties de l'espace d'état lors du parcours.

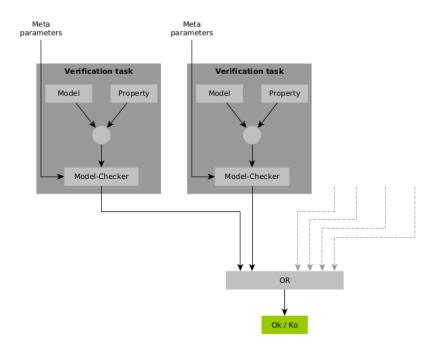

Dans le but d'augmenter la partition de l'espace d'état vérifiée, Holzmann propose l'approche swarm [7][23]. Cette approche, esquissée dans la figure 1.2, consiste à combiner les résultats de plusieurs tâches de vérification, effectuées sur le même modèle, en faisant varier les méta-paramètres de ces tâches. Ces paramètres sont choisis pour leur influence sur la partition de l'espace d'état couverte par chaque tâche de vérification, la seed utilisée par la fonction de hachage du Bloom Filter en est un exemple.

FIGURE 1.2 – Vérification swarm : Vue conceptuelle

Cette approche, orthogonale et complémentaire aux techniques d'abstraction ou d'optimisation algorithmique, montre des résultats intéressants en termes de couverture, permettant la vérification d'espaces d'états de grande taille. Holzmann montre en 2013[24] des gains significatifs de couverture par l'utilisation de la vérification swarm intégrée dans le model-checker SPIN. Cette technique a par ailleurs été intégrée dans d'autres outils de vérification très utilisés, comme Java pathfinder[25].

Une caractéristique majeure de l'approche swarm est l'indépendance complète des tâches de vérification : Ces dernières ne sont définies que par leurs méta-paramètres, sans communication entre-elles. Ce point en fait une approche intrinsèquement concurrente, permettant une distribution des calculs sur des platformes de calcul parallèles multi-coeur ou multi-processeur.

L'approche swarm permet donc la vérification de modèles de taille très importante avec un volume mémoire faible - rapporté à la taille de l'espace d'état. Elle exploite pour cela deux leviers importants que sont la compacité mémoire offerte par l'utilisation d'un Bloom filter pour stocker l'espace d'état, associé à la diversification du parcours de l'espace d'état par le changement des méta-paramètres (algorithmes, seeds). La contrepartie de cette meilleure scalabilité est un cout en termes de calcul très important : dans un cas

typique, le nombre de tâches de vérification exécutées se chiffre en dizaines de milliers[6].

### 1.3 Présentation synthétique des algorithmes

Le Model-Checking fournit une technique de preuve automatique générique et puissante basée sur l'analyse de l'espace d'état sous-jacent à l'exécution d'un modèle. Son applicabilité est basée sur l'hypothèse que le modèle, vu comme un système de transition, induit un espace d'état fini qui peut être énuméré de manière exhaustive.

Cette section propose une formalisation abstraite et générique des algorithmes de vérification pour la sûreté principalement. Le cas des algorithmes de vivacité sera traité succinctement.

### 1.3.1 Formalisation abstraite des algorithmes d'atteignabilité

Visant à proposer une cadre de raisonnement générique, cette section propose une spécification abstraite des algorithmes de Model-Checking pour la sûreté.

Dans le cadre de ce chapitre, on s'intéresse à la résolution algorithmique du problème suivant : vérifier si un programme satisfait une propriété de sûreté. Il s'agit par exemple de vérifier si le programme ne se bloque pas, ou si un certain comportement indésirable n'arrive pas. Pour ce faire, il est d'abord nécessaire de préciser la définition d'un programme. On modélise ici un programme informatique comme un système de transitions. Ce système, prends ainsi la forme d'un graphe orienté, dont chaque noeud représente les valeurs de l'ensemble des variables du système. Chaque arc, ou transition, corresponds à la modification d'une ou plusieurs variables du système.

Si l'on considère un programme qui termine exprimé dans un langage d'implémentation classique, comme C, Python, .., l'exécution du programme est déterministe. Aussi, le graphe représentant le système état-transition du programme est purement linéaire. Cependant, le modèle considéré doit être fermé, ie, n'avoir ni entrées, ni sorties. Un tel programme est donc composé avec un environnement d'exécution, non déterministe, qui lit les sorties et génère les entrées.

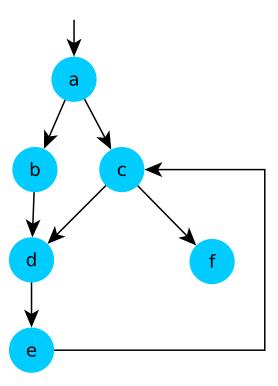

On se base donc dans la suite sur un modèle exprimé sous la forme présentée dans la figure 1.3.

### Spécification du modèle vérifié

La figure 1.3 présente l'implémentation d'un modèle simple exprimé en TLA+[26], langage proposé par L. Lamport pour décrire le comportement temporel de systèmes. Ce modèle simple est composé de trois fonctions principales, que l'on peut considérer comme l'interface publique d'un modèle.

FIGURE 1.3 – Modèle : Interface

```

A simple model S \triangleq [a \mapsto \{\text{"b"}, \text{"c"}\} \\, b \mapsto \{\text{"d"}\} \\, c \mapsto \{\text{"f"}, \text{"d"}\} \\, d \mapsto \{\text{"e"}\} \\, e \mapsto \{\text{"c"}\} \\, f \mapsto \{\}]ini \triangleq \{\text{"a"}\} \\ -next(x) \triangleq S[x]next(A) \triangleq \text{UNION } \{-next(i) : i \in A\} \\ -isSafe(x) \triangleq \text{If } x = \text{"n" THEN FALSE ELSE TRUE}isSafe(N) \triangleq \forall i \in N : \_isSafe(i)

```

La fonction ini renvoie l'ensemble, non vide, des états initiaux du système. On définit ensuite la relation de transition du système sous la forme de la fonction  $\_next(x)$ . Cette fonction, pour un état source passé en argument, renvoie l'ensemble des successeurs de cet état. Ces deux fonctions sont suffisantes pour décrire l'évolution du modèle vérifié. Pour vérifier des propriétés, il convient d'enrichir ce modèle avec la fonction  $\_isSafe(x)$  modélisant la propriété vérifiée, renvoyant, pour un état donné en entrée, son statut vis-à-vis de la propriété vérifiée (est-il sûr, ou viole t-il la propriété).

Ces deux dernières fonctions  $\_next$  et  $\_isSafe$  sont des fonctions internes à notre spécification. En elles sont utilisées en pratique via les fonctions next et isSafe qui ne sont que des sucres syntaxiques, permettant de travailler sur des ensembles. La fonction next(A) renvoie l'ensemble des états successeurs d'un ensemble d'état, et la fonction isSafe(A) envoie la conjonction de la fonction  $\_isSafe(x)$  sur l'ensemble A, ie renvoie faux si au moins un état de l'ensemble A viole la propriété.

Ce triplet de fonctions encapsule le comportement du modèle. On présente dans la

suite une spécification des algorithmes de Model-Checking, permettant d'en dériver par la suite, une architecture générique présentée au chapitre 2.

### Spécification des algorithmes

La spécification 1.4 propose une spécification abstraite d'un algorithme d'atteignabilité, exprimée dans le langage TLA+. Ce langage de haut niveau est utilisé principalement pour la modélisation de programmes informatiques et de systèmes concurrents et/ou distribués. Ce formalisme permet principalement la description d'ensembles et leurs relations.

Après avoir présenté la formalisation d'un modèle simple, que l'on peut résumer par son API publique - par convention de nommage - exprimée sous la forme de deux fonctions. Ces fonctions modélisent la relation de transition du modèle : next(A) qui renvoie l'ensemble des états successeurs à partir d'un ensemble d'états sources, et ini() qui renvoie l'ensemble des états initiaux du modèle considéré. A ces deux fonctions, on associe une fonction isSafe(N), qui encapsule le prédicat à vérifier sur les états composites.

Dans cette formalisation, le terme *état* fait référence à l'état composite, concaténation de l'état du modèle vérifié et de sa propriété, supposant ainsi que la composition de ces deux automates a été effectuée a priori.

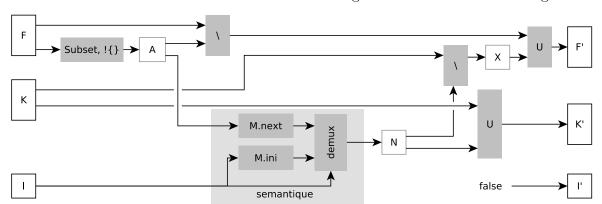

La figure 1.4 propose une abstraction des algorithmes d'atteignabilité proposés dans la littérature sous la forme d'une spécification générique.

Cette spécification se base sur la définition de deux ensembles :

- Un ensemble contenant les états déjà visités par l'algorithme Known noté K

- Un ensemble contenant les états dont les successeurs n'ont pas encore été visités Frontier noté F.

Associés à ces deux ensembles, deux variables de contrôle - booléennes - sont définies : I et S. Elles seront décrites lors de la description de la spécification ci-après.

La spécification des algorithmes d'atteignabilité est définie par la clause  $Spec \triangleq Init \wedge \Box [Next]_{\langle K,F,I,S \rangle}$ .

Considérons tout d'abord l'opérateur  $\square$ . Cet opérateur de la logique temporelle affirme que la formule donnée en argument est toujours vraie. Aussi, la formule  $\square F$  affirme que la formule F est toujours vraie, ie que F est vraie à tous les pas d'exécution. Dans la clause Spec, l'opérateur  $\square$  porte sur la clause  $Next = Step \vee TheEnd$ , qui respectivement correspondent à l'exécution d'un "pas" de l'algorithme, ou à l'atteinte de la condition de terminaison. Cette formule peut se traduire en langage naturel comme "Après avoir

$\wedge I' = \text{False}$

$Spec \stackrel{\triangle}{=} Init \wedge \Box [Next]_{\langle K, F, I, S \rangle}$

$Next \stackrel{\triangle}{=} Step \lor TheEnd$

$\wedge S' = S \wedge M! isSafe(N)$

Figure 1.4 – MODULE  $r\_frontier\_nd\_v2\_safety$ EXTENDS TLC $M \stackrel{\Delta}{=} \text{Instance } model$ VARIABLES K, F, I, S $Init \stackrel{\triangle}{=} K = \{\}$  $\land F = \{\}$ I = TrueS = True $(\neg I \land F = \{\} \land \text{UNCHANGED } \langle K, F, I, S \rangle) \lor \neg S$  $TheEnd \triangleq$  $Step \triangleq \exists A \in SUBSET F :$  $(I \lor A \neq \{\})$  $\wedge$  LET  $N \triangleq \text{If } I \text{ THEN } M! ini \text{ ELSE } M! next(A)$ IN  $K' = K \cup N$  $\wedge F' = (F \setminus A) \cup (N \setminus K)$

exécuté la clause Init, exécute Step tant que TheEnd n'est pas atteint.". Il est à noter que la clause TheEnd est terminale dans la mesure où elle ne comprends pas d'assignation.

La formule Init définit l'initialisation de l'algorithme. Si l'on fait un parallèle avec l'implémentation d'un algorithme de vérification, cette étape corresponds au tirage des états initiaux du modèle, avant de parcourir transitivement l'espace d'état. Cette étape assigne l'ensemble vide aux ensembles K et F, et définit une variable booléenne I, initialisée à la valeur true. Cette variable de contrôle permettra de différentier le premier pas d'exécution, lors duquel les états initiaux du modèle sont tirés, de la suite de l'exécution, lors de laquelle les états successeurs sont demandés au modèle. Elle ne sera vraie que lors de ce premier pas d'exécution.

Définissons ensuite la terminaison de l'algorithme : L'algorithme termine lorsque plus aucun état n'est en attente d'être visité. Ces états sont représentés par l'ensemble F, d'où la condition :  $F = \emptyset$ . Il est cependant nécessaire de distinguer la phase d'initialisation,

en effet, lors de la première "itération" de l'algorithme, l'ensemble F est vide, avant d'y assigner les états initiaux M!ini. Cette distinction nécessite l'introduction de la variable booléenne I, dont la valeur true désigne "Les états initiaux n'ont pas encore étés tirés". Cette variable est initialisée à true, et est assignée à false dès la première itération de l'algorithme, matérialisée par la clause Step:I'=FALSE. Elle reste donc vraie uniquement lors de cette première phase. La clause TheEnd est donc enrichie de la condition  $\neg$  pour prendre en compte ce cas particulier de l'initialisation. Pour finir, il est nécessaire d'imposer que rien ne change : Si F peut gagner des états après avoir été vide, alors la terminaison n'est pas encore atteinte.

Considérons maintenant un "pas" d'exécution de l'algorithme, défini par la clause Step. On commence par considérer un sous-ensemble A de F, qui correspondent aux états traités au cours du pas d'exécution courant de l'algorithme. Cet ensemble A est donc retiré de l'ensemble F, représentant l'ensemble d'états à traiter ultérieurement :  $F' = F \setminus A$ . Une requête est alors faite au modèle M pour obtenir les successeurs de A. On définit alors un ensemble intermédiaire N - Neighborhood (voisinage) - contenant ces états successeurs considérés à cette itération de l'algorithme.

Deux cas sont alors à distinguer :

- Si N contient au moins un état noté unsafe par le modèle, l'algorithme termine. Ce comportement est obtenu via le booléen S, qui est ajouté aux conditions de terminaison définies dans la formule TheEnd. Ce dernier prend la valeur true si un état de N est reconnu comme non sûr.

- Dans le cas contraire, les ensembles F et K sont rafraîchis des états traités au cours de cette itération : L'ensemble K, représentant les états déjà parcourus, ie les états dont on a déjà vérifié la sûreté, est étendu des états de N venant d'être vérifiés. L'ensemble F, représentant toujours les états à parcourir est lui aussi mis à jour, y ajoutant les états  $N \setminus K$ , qui correspondent aux états nouvellement identifiés, dont les successeurs n'ont pas encore été traités.

Cette formalisation spécifie la dynamique de parcours d'un algorithme d'atteignabilité arbitraire. Dans ce cadre, une exécution - définie comme un chemin dans l'espace d'état depuis un état initial jusqu'à un état terminal - correspond à une discipline de parcours appliquée à un modèle. Cette abstraction des algorithmes d'atteignabilité définit une famille d'algorithmes pour la vérification de propriétés de sûreté.

### 1.3.2 Algorithmes exhaustifs

La vue abstraite des algorithmes d'atteignabilité nous permet de poser un cadre de réflexion commun, décrivant un ensemble très large de parcours applicables au modèle considéré. Dans ce cadre, cette spécification peut être raffinée pour construire la spécification d'un algorithme particulier.

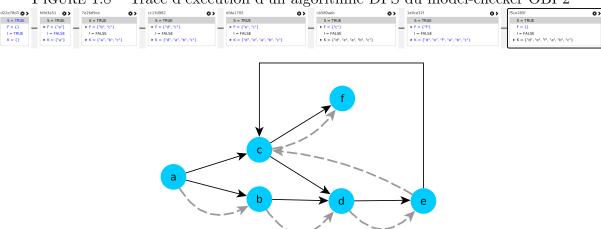

On considère comme support de raisonnement un modèle simple, composé de 6 états, comportant un cycle, et un *deadlock*. La figure 1.5 présente l'espace d'état du modèle considéré, dont l'implémentation dans le formalisme précédemment présenté est décrite dans la figure 1.3. C'est par ailleurs sur ce modèle que les traces d'exploration présentées ci-après seront construites, par le biais du model-checker OBP[27].

FIGURE 1.5 – Représentation de l'espace d'état du graphe considéré

La figure 1.6 montre les premiers pas d'éxecution de l'exploration. On note que l'espace d'état est un graphe non-déterministe : depuis le troisième état, trois pas d'exécution différents peuvent être effectués. Pour rendre cette exploration déterministe, et ainsi obtenir un parcours particulier du graphe, la spécification doit être précisée : depuis n'importe

quel état, une seule action doit pouvoir être effectuée. On se propose ici d'illustrer cette procédure de raffinement en présentant quelques algorithmes typiquement utilisés pour la vérification de propriétés de sûreté.

Un premier point important à préciser dans la spécification est l'ordre de production des successeurs par la sémantique. En effet, parler de discipline de parcours d'un graphe, que ce soit BFS, DFS, ou autre, n'a de sens que pour un ordre donné de production des successeurs pour chaque état : Pour un même état, le modèle doit renvoyer l'ensemble de ses successeurs toujours dans le même ordre.

#### **BFS**

Le premier raffinement présenté est celui permettant de construire un parcours en largeur, son implémentation étant la plus proche de l'expression de la spécification. Cet algorithme est principalement utilisé pour sa capacité à proposer des contre-exemples courts [28].

cc13d982 0> S = TRUE F = {"d", "c"} I = FALSE ▶ K = {"d", "a", "b", "c"} d22e78d3 🕿 🗲 fdfd3e51 7e26d9ce 5e421aa **@**> **@**> **Ø**> S = TRUES = TRUES = TRUES = TRUE▶ F = {"d", "f", "b"} ► F = {"b", "c"}  $F = \{\}$ ▶ F = {"a"} I = TRUEI = FALSEI = FALSEI = FALSE $K = \{\}$ ▶ K = {"a"} ► K = {"a", "b", "c"} ▶ K = {"d", "f", "a", "b", "c"} 8a3da258 **@>** S = TRUE ▶ F = {"d", "f"} I = FALSE ► K = {"d", "f", "a", "b", "c"}

FIGURE 1.6 – Premiers pas d'exécution de la simulation

Dans son implémentation classique, un parcours en largeur se base sur une file d'attente - First In First Out - pour stocker les états en attente d'être visités. Ces états

correspondent exactement aux états de la frontière de l'exploration : tous les états contenus dans la FIFO d'un BFS sont des états dont les prédécesseurs ont été parcourus, mais dont les successeurs ne l'ont pas encore été. Ces états correspondent exactement aux états de l'ensemble Frontière - F - défini comme variable de la spécification.

Ils sont cependant décrits comme un ensemble non ordonné: il est nécessaire de préciser ce comportement, en y ajoutant une relation d'ordre, définie comme l'ordre d'insertion dans l'ensemble. Notons que l'appel à la relation de transition  $M!next(\_)$  renvoie un ensemble. Ceci étant, la définition du raffinement est ici naturelle : l'ensemble de successeurs renvoyé par la fonction  $M!next(\_)$  est supposé ordonné, les successeurs sont donc ajoutés dans cet ordre à la frontière.

Une fois cette précision effectuée, la spécification d'un parcours en largeur se résume simplement à contraindre la sélection de l'ensemble A d'états à traiter dans l'itération courante - défini initialement comme un sous-ensemble de F - à un singleton contenant l'état le plus "vieux" dans la frontière ( la tête de la FIFO ).

FIGURE 1.7 – Trace d'exécution d'un algorithme BFS du model-checker OBP2

Ce parcours est illustré dans la figure 1.7, sur laquelle les liens noirs représentent les transitions entre les états, et les flèches pointillées grisées décrivent le parcours effectué par l'algorithme.

A l'état initial, les ensembles F et N sont vides, et la variable I est vraie, désignant que les états initiaux n'ont pas encore été parcourus. Les états initiaux, en l'occurrence ici, "a", sont ajoutés dans au Known, et à la Frontière.

L'état le plus vieux de la Frontière, "a", est sélectionné et retiré de F, qui est étendue de ses successeurs "b" et "c".

L'algorithme parcours les états successeurs jusqu'à ce que l'élément "e" soit traité,

dont le successeur "c" a déjà été parcouru, et n'est donc pas ajouté dans la frontière.

A l'itération suivante, l'ensemble des états à traiter, F, est vide, et l'algorithme termine.

#### DFS

Le parcours en largeur possède intrinsèquement la propriété - majeure pour le débug - de fournir des contre-exemples de longueur minimale. Cependant, le parcours en profondeur est souvent préféré pour la vérification par Model-Checking pour des considérations d'efficacité mémoire. De plus, un parcours en profondeur permet de reconstruire le contre-exemple en se basant sur les seuls états contenus dans la pile d'états à parcourir.

Considérons tout d'abord le cas d'un parcours en infixe. Ce dernier se construit de manière analogue au parcours précédemment présenté, en imposant une relation d'ordre sur la Frontière. La seule différence entre ces deux parcours est la sélection de l'ensemble d'états à traiter dans l'itération courante : A. Dans le cas d'un DFS infixe, l'ensemble A sera toujours un singleton contenant l'état le plus récemment ajouté dans la Frontière.

Le parcours infixe, présenté à titre pédagogique, n'est cependant que rarement utilisé dans le cadre de la vérification de propriétés de sûreté. En effet, contrairement à un parcours postfixe, le parcours infixe ne permet pas la reconstruction du contre-exemple sans utiliser une structure de données additionnelle (arbre de parents).

FIGURE 1.8 – Trace d'exécution d'un algorithme DFS du model-checker OBP2

Dans le cas du parcours postfixe, l'implémentation diffère légèrement de la spécification : La pile utilisée dans le cadre d'un DFS ne corresponds pas directement à la frontière, mais l'inclus. En effet, dans le cas de cet algorithme, la queue contient non seulement la frontière, mais également l'ensemble de ses prédécesseurs, jusqu'aux états initiaux. La preuve de raffinement de la spécification est moins naturelle, mais peut s'effectuer via la construction d'un observateur[29] qui reconstruit l'ensemble *frontière* de la spécification à partir des états contenus dans la pile.

Il est important de noter que l'exécution de la spécification de l'algorithme évolue de manière partiellement désynchronisée de l'implémentation : L'implémentation a besoin de plusieurs pas d'exécution avant que la spécification ne fasse un pas, chaque successeur étant traité individuellement.

### Model-Checking Borné

Dans le cadre de la vérification de modèles complexes, les algorithmes précédents peuvent être limités par leur besoin mémoire important : Le stockage de l'espace d'état nécessite un volume mémoire qui dépasse souvent les capacités mémoires de la plateforme d'exécution.

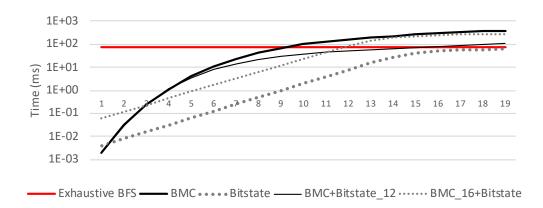

Pour contourner cet écueil, une stratégie peut être de ne rechercher que des contreexemples de longueur *au plus n*. Cette approche, partielle, présente l'intérêt d'une forte compacité mémoire, mais ne permet que difficilement de s'assurer que l'intégralité de l'espace d'état a été parcouru sans analyse complexe du modèle.

Une solution naturelle pour implémenter une telle recherche est l'implémentation d'un parcours en largeur dont la profondeur est limitée. Dans ce cadre, la représentation explicite de l'ensemble des états parcourus, nécessaire dans l'implémentation des deux algorithmes précédents pour assurer la terminaison de l'algorithme <sup>1</sup>, n'est plus nécessaire : la terminaison est assurée par la borne imposée sur la longueur du contre-exemple.

Aussi, le nombre d'états stockés pour assurer la terminaison peut être drastiquement réduit : Il n'est plus nécessaire que de stocker l'étage de profondeur en train d'être découvert, pour filtrer les états dupplicats parmi les successeurs de la frontière.

Dans ce cas, l'implémentation usuelle consiste à exploiter une file d'attente à deux étages, l'un stockant les états de l'étage courant - en train d'être dépilé - et l'autre stockant les états de l'étage suivant, successeurs de l'étage courant. Dans l'implémentation, l'ensemble stockant les états déjà parcourus ne contient que les états de l'étage suivant, et est vidé lorsque l'étage courant est entièrement visité.

<sup>1.</sup> L'espace d'état est un graphe potentiellement cyclique

Cet algorithme raffine également la spécification proposée, les ensembles K et F peuvent être reconstruits par deux observateurs, respectivement stockant tous les états parcourus à ce point de l'exploration, et concaténant les deux étages de la file d'attente utilisée dans l'implémentation.

FIGURE 1.9 – Trace d'exécution d'un algorithme DFS du model-checker OBP2

### Algorithme symbolique

La section précédente a évoqué deux axes principaux pour repousser l'explosion combinatoire : l'abstraction du modèle d'une part, et l'optimisation algorithmique d'autre part. Cette disparité est valable dans le cadre du Model-Checking dit *explicite*, forme dans laquelle l'analyse est effectuée sur le modèle représenté explicitement.

A la fin des années 90[19], Mcmillan proposa un résultat prometteur : L'utilisation d'une représentation symbolique de la relation de transition - sous forme d'arbres binaires de décision(BDD) - permet une représentation bien plus compacte en mémoire que les techniques explicites, permettant ainsi de vérifier des modèles comportant un nombre extrêmement large d'états, gagnant plusieurs ordres de grandeur en scalabilité.

L'implémentation symbolique d'un Model-Checker est similaire à la version explicite. Une différence importante est cependant à noter : l'algorithme ne travaille pas sur un état explicite, mais sur un ensemble d'états représenté par un arbre de décision. L'implémentation de la fonction  $M!next(\_)$  renvoie donc un ensemble, dont l'intersection et l'union avec l'ensemble K est calculée pour obtenir respectivement la nouvelle valeur des ensembles F et K, représentés dans le même formalisme. Ce type de parcours peut s'apparenter au parcours en largeur borné présenté précédemment, la différence majeure étant que les états sont traités de manière ensembliste, par des transformations algébriques sur

les formules booléennes les représentant, et non par énumération. La figure 1.10 illustre un de ces raffinements de la spécification.

FIGURE 1.10 – Trace d'exécution d'un algorithme symbolique du model-checker OBP2

#### Synthèse partielle

L'explosion combinatoire est une caractéristique intrinsèque du Model-Checking. L'effort de recherche important déployé pour trouver des contre-mesures a mené à la proposition de multiples algorithmes, présentant chacun un intérêt dans une situation particulière : minimisation ou capacité de reconstruction du contre-exemple, scalabilité. Cependant, ces algorithmes partagent une structure commune, illustrée ici au travers d'une spécification abstraite.

Cette structure commune des algorithmes, associée au besoin de multiples parcours pour mener à bien un effort de vérification, a influencé fortement l'architecture de Model-Checkers modernes, comme Divine3[11], LTSmin[30], ou OBP2[27].

Avec peu de modifications, cette spécification abstraite peut être généralisée pour illustrer aussi des algorithmes partiels.

#### 1.3.3 Extension aux algorithmes de vérification partielle

La spécification précédemment présentée se veut être un outil de raisonnement, de manière à construire une architecture générique supportant des algorithmes multiples, ainsi qu'à, dans la suite, illustrer la généricité des architectures proposées. Cependant, cette formulation de la spécification ne supporte qu'une sous-partie des algorithmes utilisables pour effectuer des tâches de vérification sur un modèle, constituée des algorithmes exhaustifs. On propose dans cette section une généralisation à des algorithmes partiels, offrant une compacité mémoire fortement améliorée par rapport à leurs versions exhaustives.

Les algorithmes de vérification explicites présentés précédemment reposent sur une représentation déterministe d'ensemble pour stocker l'espace d'état : on a donc une relation un-à-un entre les états effectivement stockés dans l'ensemble abstrait K, et son implémentation, généralement effectuée par une table de hachage dans le cas du Model-Checking explicite. Cette forme de représentation d'ensemble est intrinsèquement gourmande en mémoire : chaque élément ajouté est stocké explicitement, sans compression. Plusieurs techniques ont été proposées pour augmenter la compacité mémoire de ces ensembles (nombre d'états stockables par octet)[20][7][21]. Elles ont en commun de ne pas stocker les éléments directement, mais l'image de ces derniers par une fonction injective (fonction de hachage). Aussi, le test d'appartenance d'un état à l'ensemble d'états connus est dégradé : seule son image par la fonction f est prise en compte pour décider son appartenance. Cette particularité induit la possibilité d'occurrence de faux positifs : deux états dont l'image par f est identique ne pourront être différentiés lors du test d'appartenance.

Historiquement, l'exploitation de ce type de représentation compressée a été proposée en 1995 par Stern & Dill. La technique proposée, communément appelée hash compaction, consiste au stockage direct du hash des états dans une table de hachage, permettant ainsi de réduire l'occupation mémoire à quelques octets par état. Cette variation a été implémentée dans le Model-Checker  $Mur\phi[31]$ , ainsi que dans la première implémentation d'un model-checker matériel : PHAST [31][32].

La recherche de compacité mémoire a été ensuite poussée plus avant par Holzmann, proposant la technique du bitstate hashing [20]. Cette technique repose sur une représentation de l'ensemble fontière par un filtre de Bloom. Dans ce cas, l'ensemble est implémenté sous la forme d'une table de booléens, dont la valeur vraie corresponds à la présence de(s) l'état correspondant. Cette représentation présente l'intérêt d'une compacité mémoire extrême, pouvant être inférieure à 1bit/état dans le cas où plusieurs fonctions de hachage sont utilisées pour l'implémentation du filtre de Bloom [33].

D'un point de vue de la spécification ces algorithmes, la modification à effectuer par rapport à la spécification initiale est naturelle :

La figure 1.3.3 présente une généralisation de la spécification pour prendre en compte ces algorithmes partiels. L'ensemble K ne contient ici que l'image des éléments visités au

```

Step \triangleq \exists A \in \text{SUBSET } F:

(I \lor A \neq \{\})

\land \text{ LET}

N \triangleq \text{ IF } I \text{ THEN } M! ini \text{ ELSE } M! next(A)

IN

K' = K \cup hashFct(N)

\land F' = (F \setminus A) \cup \{x \in N : hashFct(x) \notin K\}

\land I' = \text{FALSE}

\land S' = S \land M! isSafe(N)

```

FIGURE 1.11 – Extension de la spécification 1.4 aux parcours partiels

travers d'une fonction de hash hashFct. De manière analogue à la spécification initiale, l'ensemble Fontière est calculé en soustrayant les états traités pendant le cycle courant, et en y ajoutant les successeurs non présents dans l'ensemble d'états visités.

Cette spécification générale, permettant de formaliser les algorithmes de vérification partielle, est plus général que la version précédemment présentée : La preuve de raffinement est immédiate en représentant l'ensemble K en utilisant hashFct = Identite.

#### 1.4 Enjeux de performance et solutions matérielles

Le milieu des années 2000 a sonné la fin le la Loi de Dennard, conséquence de la loi de Moore prédisant l'augmentation de la fréquence des circuits parallèlement à l'augmentation de leur niveau d'intégration. Aussi, l'augmentation de la puissance de calcul s'est traduite par l'introduction, puis la généralisation des processeurs multi-coeurs.

Dans le même temps, la complexité et la criticité des système n'a cessé de croitre, ainsi que le besoin de vérification. Ce constat a motivé un effort de recherche important visant à accroitre la performance en plus de la scalabilité des outils de Model-Checking.

#### 1.4.1 Plateformes de calcul parallèles pour le Model-Checking

Les travaux portant sur la parallélisation des algorithmes de Model-Checking peuvent se classer en trois catégories, correspondant aux plateformes de calcul ciblées : multicoeur/multi-processeur, distribuée, et plus récemment SIMD, avec l'exploration des pos-

| sibilités offertes | par le | parallélisme | massif offert | par les | GP-GPU. |

|--------------------|--------|--------------|---------------|---------|---------|

|--------------------|--------|--------------|---------------|---------|---------|

|                     | Distribué                | Mémoire partagée         | GPU            | FGPA     |

|---------------------|--------------------------|--------------------------|----------------|----------|

| NFA                 | [34] [35] [36]           | [37] [38]                | [39] [40] [41] | [6] [32] |

| $\omega$ -automates | [42] [43] [44] [45] [46] | [47] [48] [49] [50] [51] | [52] [53]      | N.A.     |

FIGURE 1.12 – Parallélisation des algorithmes de Model-Checking

La figure 1.12 recense un certain nombre de travaux visant la parallélisation des algorithmes de Model-Checking. Ces travaux sont classés en fonction du modèle de programmation utilisé - mémoire distribuée, mémoire partagée, SIMD et FPGA - ainsi qu'en fonction du type de propriétés vérifiées. Comme précisé précédemment, cette distinction implique le type d'algorithme utilisé : un parcours d'atteignabilité est suffisant pour la vérification de propriétés de sûreté, mais un algorithme de détection de cycles est nécessaire pour la vérification de propriétés plus générales, représentées par des automates  $\omega$ -réguliers comme les automates de Büchi, par exemple.

Les systèmes distribués sont une cible naturelle pour l'accélération du Model-Checking. L'intérêt de cette approche est liée principalement à l'augmentation linéaire du volume mémoire disponible avec le nombre de machines utilisées. Cependant, un point d'attention critique pour la mise au point d'algorithmes ciblant de telles plateformes réside en la minimisation des communications mises en jeu pendant l'exécution.

L'accélération du Model-Checking explicite sur de tels systèmes a été initiée par les travaux de Lerda [36], suivie d'un travail important mené par l'équipe Tchèque de J. Barnat et L. Brim, qui a mené à la proposition des algorithmes MAP [42], OWCTY [44], NEGC [46].

La généralisation des systèmes multi-coeurs et multi-processeurs a constitué une opportunité importante pour la vérification : partageant la mémoire principale entre les coeurs, ces systèmes permettent une communication beaucoup moins couteuse entre des processus concurrents. La structure hiérarchique de la mémoire peut de plus être avantageusement exploitée pour accélérer le stockage des états visités [38]. De nombreux travaux ont été menés sur ce sujet dans le contexte du développement du Model-Checker LTSmin, menés par J. Van De Pol [48] [49][50][51].

La scalabilité importante des algorithmes proposés ciblant des plateformes multicoeurs suscite naturellement la question de leur scalabilité sur des plateformes massivement parallèles. Les GP-GPU - General Purpose Graphical Processing Units - sont de plus en plus utilisés pour le calcul parallèle. De plus, leur ratio consommation/performance ainsi que leur coût relativement faible en font des outils de calcul plus efficaces que les processeurs pour nombre d'applications massivement parallèles. Quelques travaux portent sur l'exploitation de ces derniers proposent des résultats prometteurs, mais sans rupture majeure par rapport aux implémentations multi-coeurs [41] [53].

Ces trois modèles de calculs - distribué, mémoire-partagée, et gpu - ont chacun fait l'objet de travaux importants, visant à accélérer le Model-Checking. A contrario, seuls deux articles traitent de l'accélération matérielle du Model-Checking via l'utilisation de FPGA.

#### 1.4.2 Accélération matérielle du Model-Checking

Les plateformes de calcul reconfigurables constituent un outil de plus en plus utilisé pour le calcul intensif. Outre le parallélisme intrinsèque et massif offert par de telles plateformes, la structure locale de la mémoire interne permet de bénéficier d'une latence en lecture et écriture constante et très faible.

Deux approches proposent l'exploitation de plateformes reconfigurables - FPGA - pour l'accélération matérielle du Model-Checking.

#### PHAST: un coeur de Model-Checking explicite reposant sur hash compaction

La première approche proposée pour l'accélération du Model-Checking explicite a été proposée en 2008, par M.E. Fuess et M. Lesser [54]. Dérivé du Model-Checker  $\operatorname{Mur} \phi$ , cette approche implémente un parcours en largeur, reposant sur la technique de  $\operatorname{hash}$  compaction [21] présentée en section 1.2.3.

Cette technique de compression permet la réduction importante du volume mémoire utilisé pour stocker l'espace d'état, en ne stockant qu'une représentation réduite des états, sous la forme de son image par une fonction de hachage. Cette technique permet de réduire l'empreinte mémoire d'un état, dans cette implémentation, 40 bits. Cette compacité mémoire est cependant obtenue au prix de l'exhaustivité du parcours.